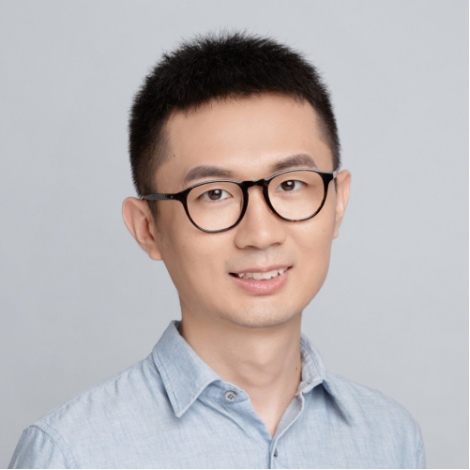

Dr. Zhiru Zhang is a Professor in the School of Electrical and Computer Engineering at Cornell University and a member of the Computer Systems Laboratory. His current research investigates new algorithms, methodologies, and design automation tools for heterogeneous computing systems. Recent publications from his group focus on the topics of high-level synthesis (HLS), hardware specialization for machine learning, and programming models for software-defined FPGAs.

Prior to joining Cornell, he earned his Ph.D. in Computer Science from UCLA and co-founded AutoESL based on his dissertation research on HLS. AutoESL was acquired by Xilinx (now AMD), and its HLS tool evolved into Vivado HLS (now Vitis HLS), which is widely used for designing FPGA-based hardware accelerators. He also holds a B.S. in Computer Science from Peking University and an M.S. in Computer Science from UCLA.